Diagramas de temporización de instrucción FFL y FFU

Los siguientes ejemplos de diagrama de temporización describen escenarios de ejecución para las instrucciones FFL (carga FIFO) y FFU (descarga FIFO).

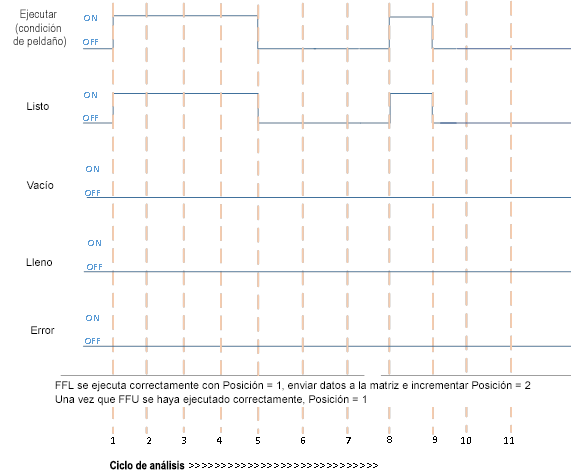

Ejecución FFL correcta seguida de ejecución de FFU correcta

Ejecución FFL correcta seguida de ejecución de FFU correcta

Ciclo de análisis | Descripción |

|---|---|

1 | La condición de línea pasa a ser Cierto cuando:

|

2,3,4 | No hay cambio en la condición de línea. |

5 | La condición de línea pasa a ser FALSO cuando:

|

6, 7 | No hay cambio en la condición de línea.

|

8 | Línea cambia a CIERTO si:

|

9 | No hay cambio en la condición de línea.

|

10, 11 | No hay cambio en la condición de línea. |

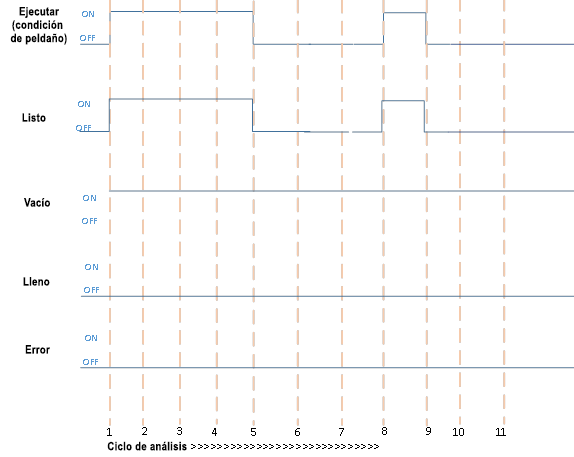

Ejecución correcta si el bit vacío es CIERTO

Ejecución correcta si el bit vacío es CIERTO

Ciclo de análisis | Descripción |

|---|---|

1 | La condición de línea pasa a ser Cierto cuando:

|

2,3,4 | No hay cambio en la condición de línea. |

5 | La condición de línea pasa a ser FALSO cuando:

|

6, 7 | No hay cambio en la condición de línea. |

8 | Línea cambia a CIERTO si:

|

9 | La condición de línea pasa a ser FALSO cuando:

|

10, 11 | No hay cambio en la condición de línea. |

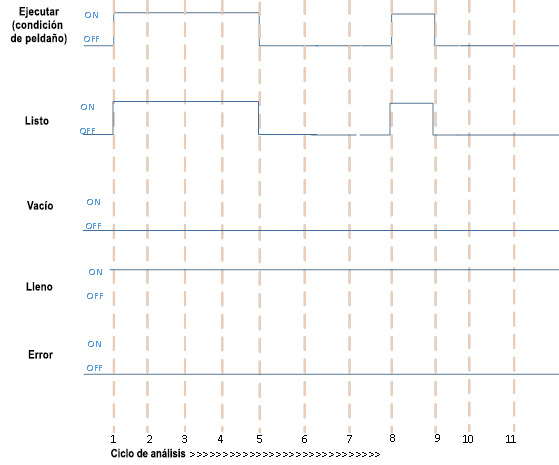

Ejecución correcta si el bit vacío es CIERTO

Ejecución correcta si el bit vacío es CIERTO

Ciclo de análisis | Descripción |

|---|---|

1 | La condición de línea pasa a ser Cierto cuando:

|

2,3,4 | No hay cambio en la condición de línea. |

5 | La condición de línea pasa a ser FALSO cuando:

|

6, 7 | No hay cambio en la condición de línea. |

8 | Línea cambia a CIERTO si:

|

9 | La condición de línea pasa a ser FALSO cuando:

|

10, 11 | No hay cambio en la condición de línea. |

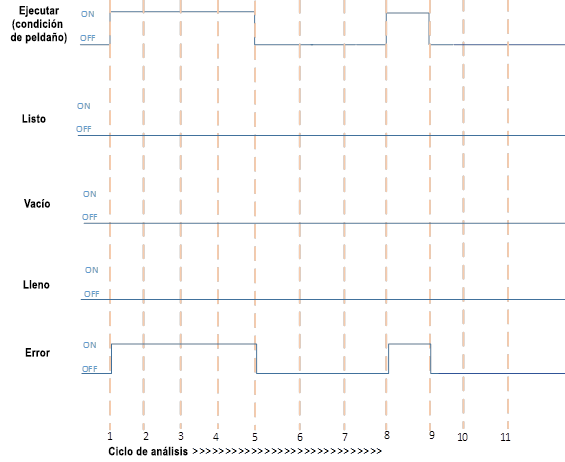

Se ha detectado un error durante la ejecución de FFL y FFU

Se ha detectado un error durante la ejecución de FFL y FFU

Ciclo de análisis | Descripción |

|---|---|

1 | La condición de línea pasa a ser Cierto cuando:

|

2,3,4 | No hay cambio en la condición de línea. |

5 | La condición de línea pasa a ser FALSO cuando:

|

6, 7 | No hay cambio en la condición de línea. |

8 | Línea cambia a CIERTO si:

|

9 | La condición de línea pasa a ser FALSO cuando:

|

10, 11 | No hay cambio en la condición de línea. |

Entregue su opinión