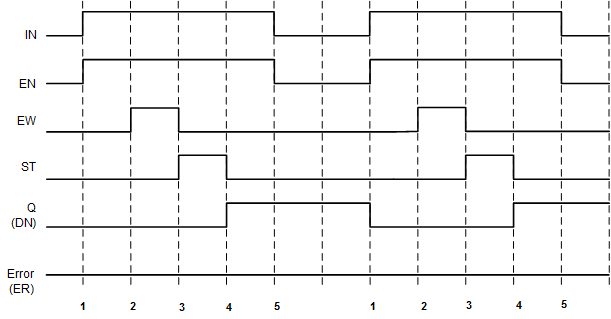

Message execution timing diagram (Rung = TRUE)

The following table describes the message conditions and bit status for each execution step identified in the timing diagram while the rung condition remains true.

Step | Message Description | Bit Status |

|---|---|---|

1 | Rung condition goes TRUE. Message execution is enabled. | EN bit is set. All other bits are cleared. |

2 | Message control buffer is acquired. At this time, input data (that is, the "data" parameter for write messages) is copied for transmission. Subsequent changes to the input data will not be reflected in the transmitted message. | EW bit is set. |

3 | Message transmission starts. | EW bit is cleared. ST bit is set. |

4 | Message response is received. | ST bit is cleared. DN bit is set. |

5 | Rung condition goes FALSE. | EN bit is cleared. |

Timing diagram for (Rung = TRUE)

Timing diagram for (Rung = TRUE)

Provide Feedback