Compiler Verification

The Compiler Verification Tool (CVT) verifies the following:

- Compiler output is correct

- Compiler output matches source code input

- Compiler output contains only the essential elements of the source code input.IMPORTANT: Other than Sequential Function Chart (SFC), all produced code is validated for use in safety applications.AADvance-Trusted SIS Workstation softwaredoes not validate SFC code.

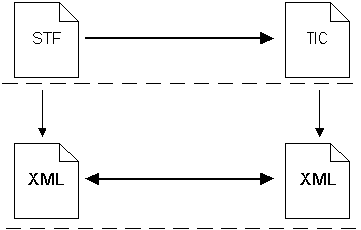

The compilation verification process compares individual program organization unit (POU) STF files with their resulting TIC code to validate the accuracy of the compilation process. The verification process starts when the compiler completes the generation of the TIC code from the STF file. The process consists of converting the STF file to an XML file and disassembling the TIC code towards another XML file, then comparing both resulting XML files for differences. Separate utilities perform the conversion of the STF file and the disassembly of the TIC code.

Code Generation |  |

Verification Process | |

Output Window | Comparison errors |

Apply the guidelines detailed in

Applying Best Practices

to make sure the CVT provides an efficient and accurate analysis of the source TIC code.

To enable the compiler verification

- From thePropertieswindow of a controller, expandCompiler Options.

- SelectEnable Compiler Verification, and then selectTrue.

- From thePropertieswindow of an FBD or LD program, selectGenerate Monitoring Symbols, and then selectTrue.

Provide Feedback