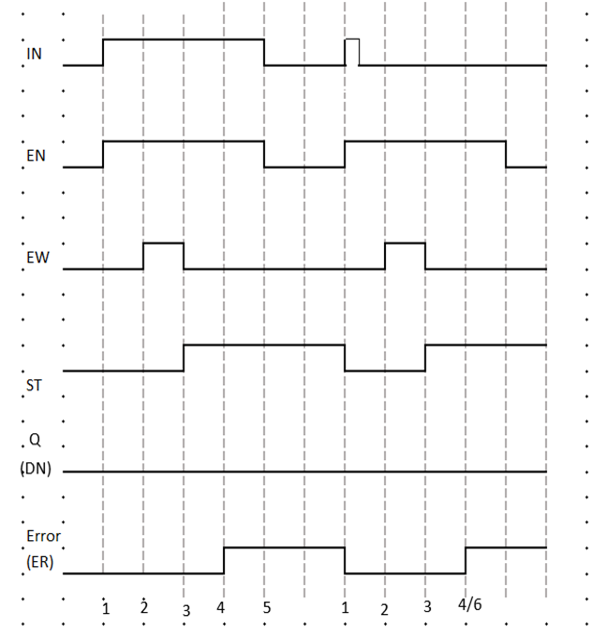

Message execution timing diagram (PCCC configuration error)

The following table describes the message conditions and bit status for each execution step identified in the timing diagram when a PCCC configuration error occurs during execution.

Step | Message Description | Bit Status |

|---|---|---|

1 | Rung condition goes TRUE. Message execution is enabled. | EN bit is set. |

2 | Message buffer is acquired. | EW bit is set. |

3 | Invalid elements exist in PCCCCfg. | ER bit is set to 1 before ST bit is set to 1. EW and ST bits do not change. |

4 | As rung condition goes FALSE. | EN, EW, and ER bits are cleared. |

Error condition diagram

Error condition when changing the number of elements in PCCCCfg to an invalid number 17

Provide Feedback